はじめに

半導体デバイス等の精密電子部品は、静電気により内部の回路が破壊されてしまうことがあります。精密電子部品の歩留まり向上や不具合低減のためには、この静電気による回路破壊を防ぐことが重要となってきます。今回は、この静電気をうまく制御し、いかにデバイス等の破壊を防ぐかについて考えていきたいと思います。

静電気とは

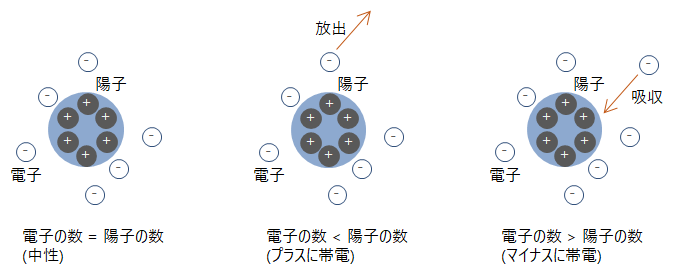

全ての物質は原子核 と電子からなる原子からできています。原子核の中にある陽子は+ (プラス) の電荷を持ち、電子は- (マイナス) の電荷を持っています。通常は陽子 (+) と電子 (-) の数が釣り合っていて、電気的に中性な状態を保っています。

原子から電子が放出されるとその原子はプラスに帯電し、電子を吸収するとマイナスに帯電します。この帯電現象が静電気の原因となります。

それでは、どのような場合に静電気が生じるのでしょうか?

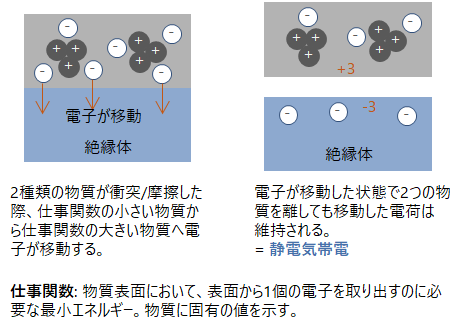

異なる2種類の物質の間に衝突や摩擦などが生じると、片方の物質からもう片方の物質へ電子が移動することがあります。電子が移動しますので、元の物質はプラスに、移動先の物質はマイナスに帯電します。この電子が移動した状態で、2つの物質を引き離しても移動した電荷は維持されるため、これら両物質は帯電した状態となります。

ESD破壊

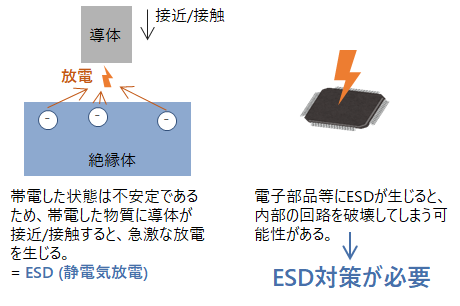

帯電した物質は非常に不安定な状態であるため、電気的に中性の状態に戻ろうとします。ですので、電気を流しやすい導体と接近もしくは接触すると、急激な放電を生じます。この現象を ESD (静電気放電) といいます。

半導体デバイス等の電子部品へESDが生じると、内部の回路を破壊してしまう可能性があります。製品の歩留まりを向上させ、また、不具合発生を低減させるためにも、製品設計や生産工程内でのESD対策は非常に重要になってきます。

対策方法

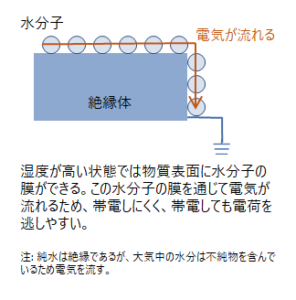

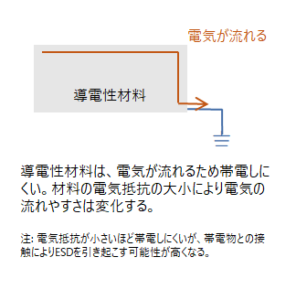

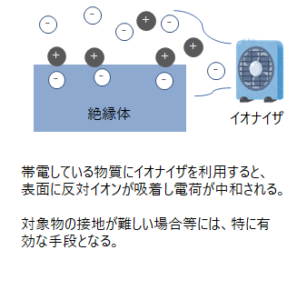

電子デバイスは設計段階で十分にESD対策はなされておりますが、それでも完全にESDによる回路の破壊を防ぐことは難しいです。そのため、電子デバイスに触れる梱包材料、搬送部品、検査治具等はもちろん、検査する人のESD対策も重要です。代表的なESDを対策としては、以下の方法が考えられます。

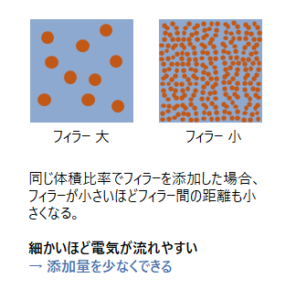

PBIアドバンストマテリアルズでは、これまで様々なスーパーエンジニアリングプラスチックと各種フィラーの複合化を行ってまいりました。その経験と実績から、スーパーエンジニアリングプラスチックに特化した導電材料の開発・製造・販売を行っております。

特に非常に細かいフィラーの添加を得意としております。細かいフィラーを使用することにより安定した物性を再現でき、微細な加工にも適した材料となっております。また、細かいフィラーを用いることにより添加量を抑えることが可能になり、摩耗時の発塵量も低減することができます。

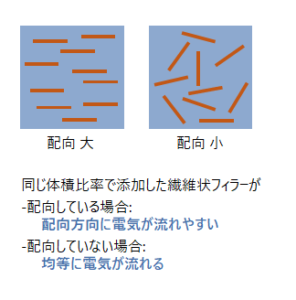

また、PBIメソッドという弊社独自の圧縮成形技術を使用すると、射出成形や押出成形素材に比べて非常に異方性の小さくなります。電気特性はもちろん、他の各種機械特性においても、素材内で均一な物性を実現しております。

次回は、ESD対策における導電性材料の表面抵抗についてお話したいと思います。

関連記事:

いま知りたいESD対策 #2 表面抵抗の測定方法